# 22nd International SPIN Symposium on Model Checking of Software

# DSVerifier: A Bounded Model Checking Tool for Digital Systems

Hussama I. Ismail, **lury V. Bessa**, Lucas C. Cordeiro Eddie B. de Lima Filho, and João E. Chaves Filho

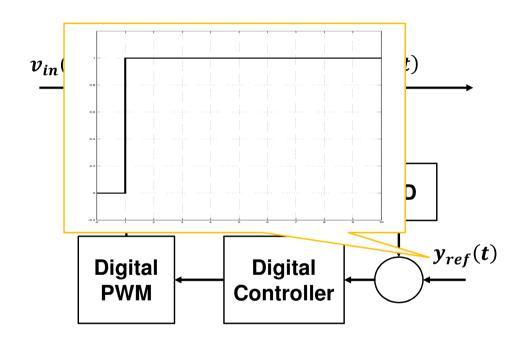

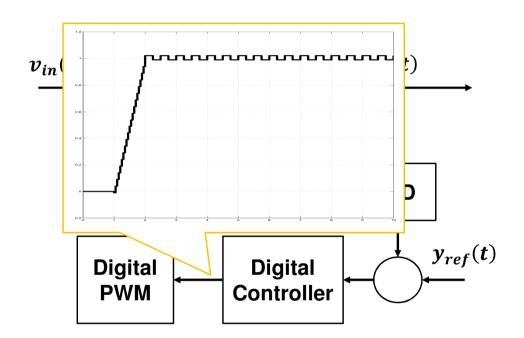

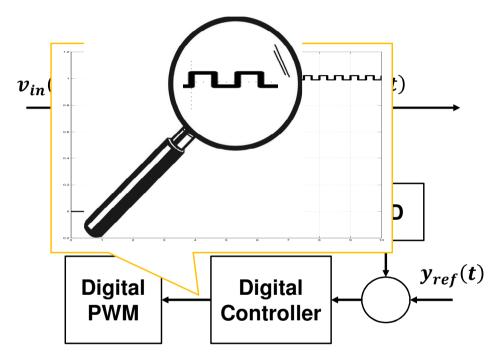

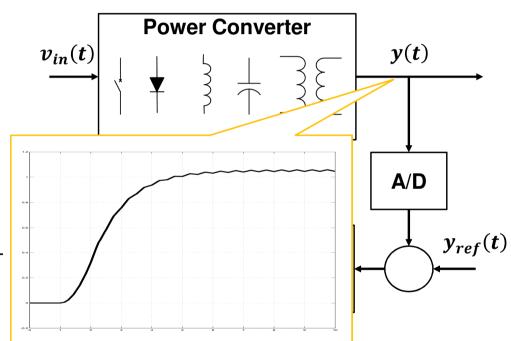

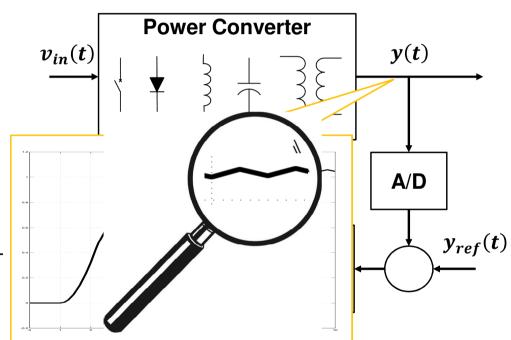

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

- Digital filters and controllers are currently replacing many analog components

- Despite several advantages, they present limitations related to finiteword length (FWL) effects

- Limit cycle oscillations (LCOs) in power converters:

- Oscillation in output voltage due to roundoff and overflows

- More energy losses and short silicon lifespan

- LCOs are almost unavoidable and difficult to be detected

- LCOs are typically detected via timedomain simulations

## **Bounded Model Checking (BMC)**

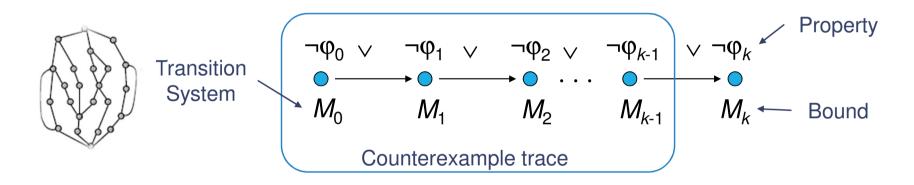

• Basic Idea: given a transition system M, check negation of a given property  $\varphi$  up to given depth k

- Translated into a VC  $\psi$  such that:  $\psi$  is satisfiable iff  $\varphi$  has counterexample of max. depth k

- BMC has been applied successfully to verify (embedded) software since early 2000's, but it has not been used to verify digital controllers

#### **Objectives**

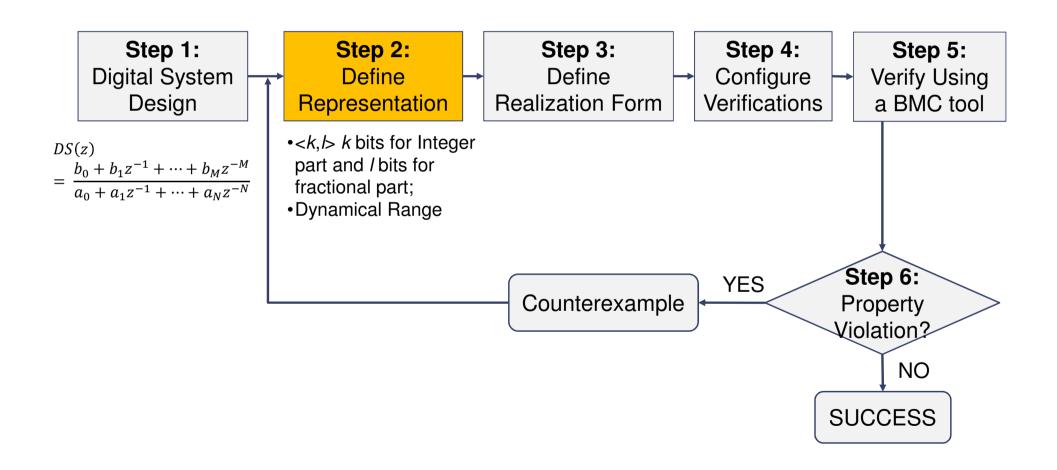

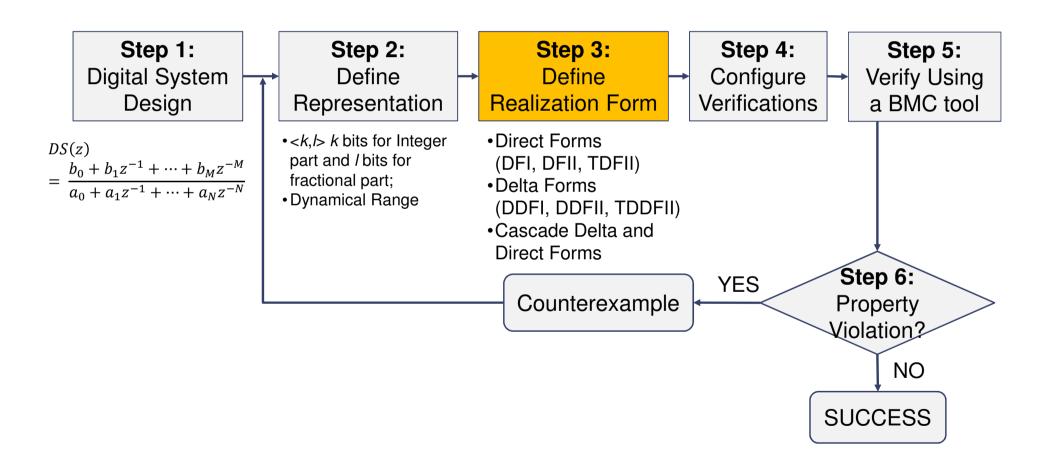

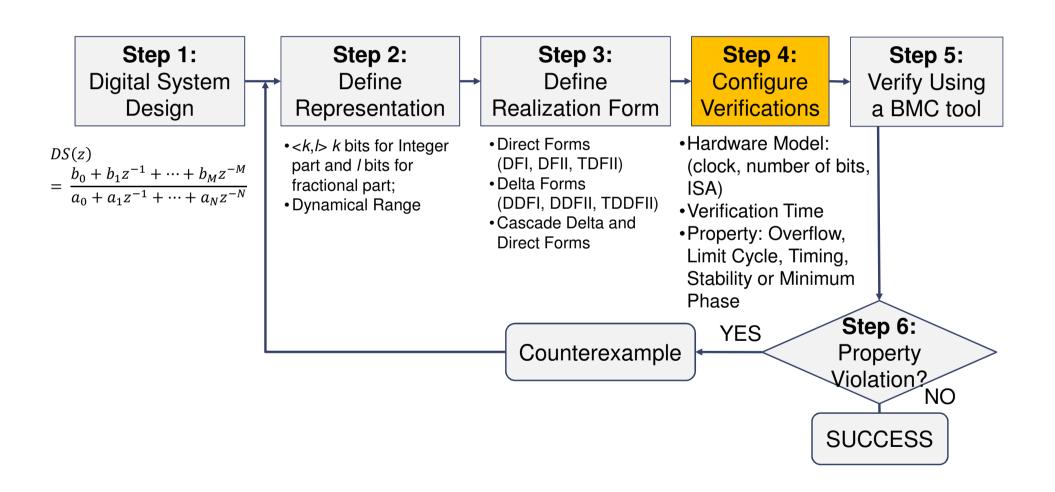

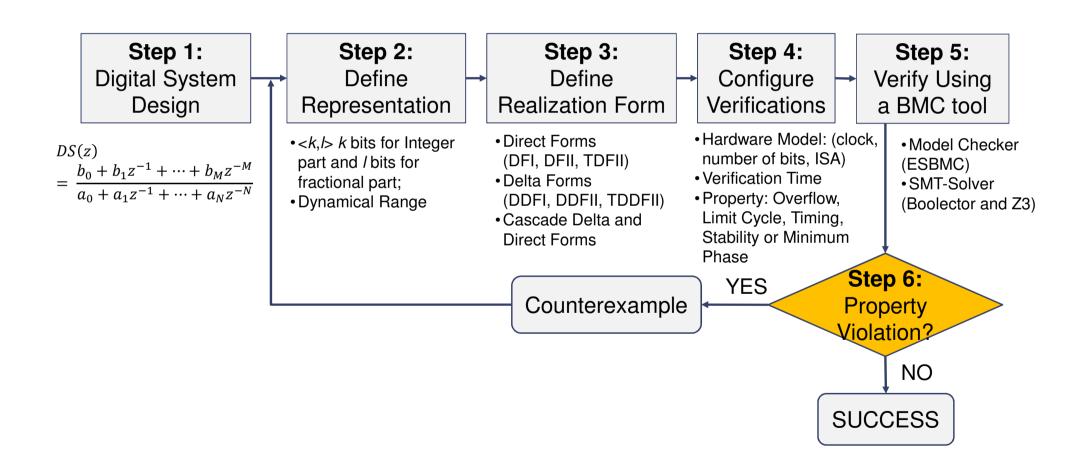

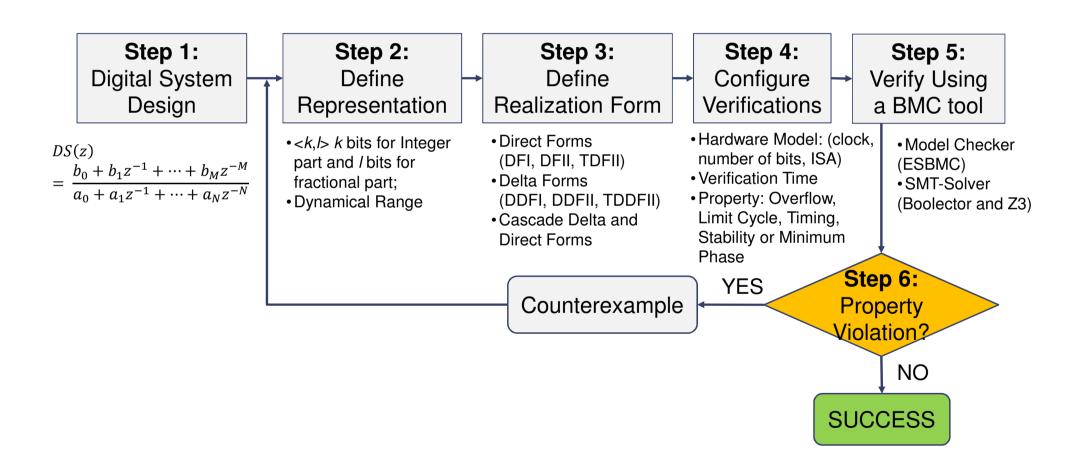

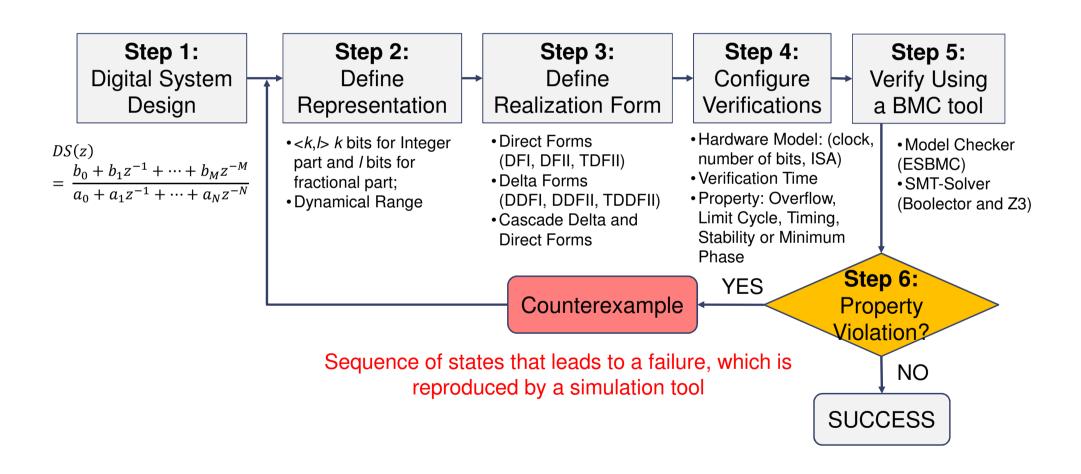

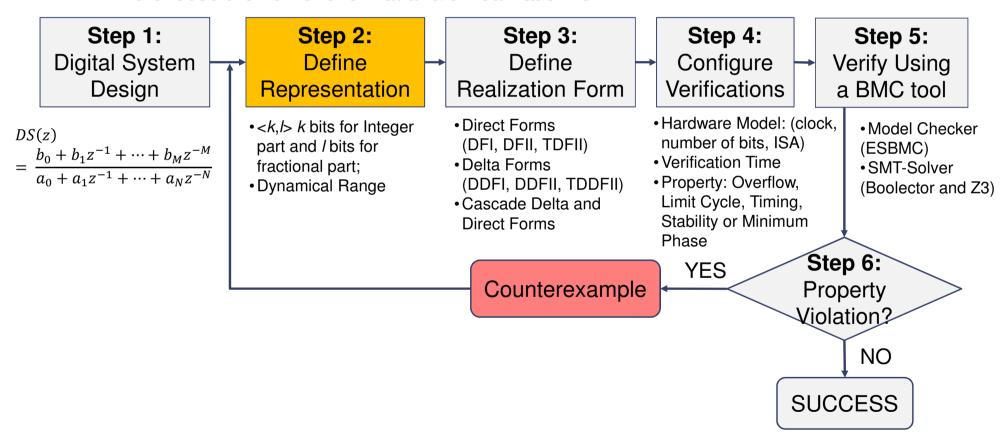

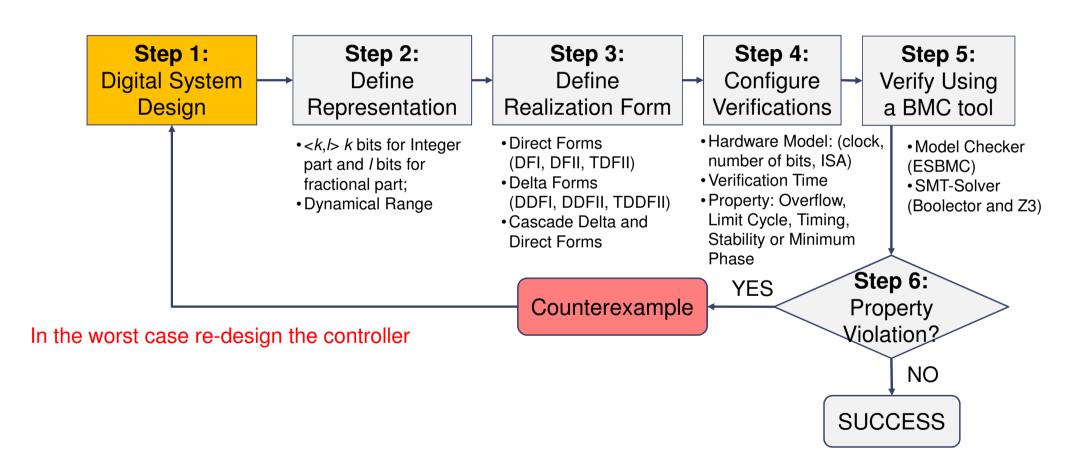

#### BMC of digital systems implementations considering FWL effects

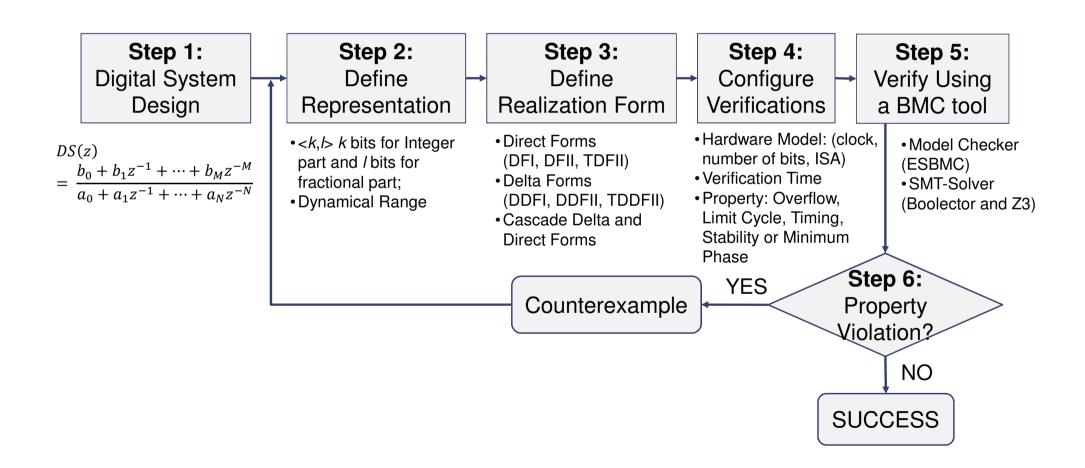

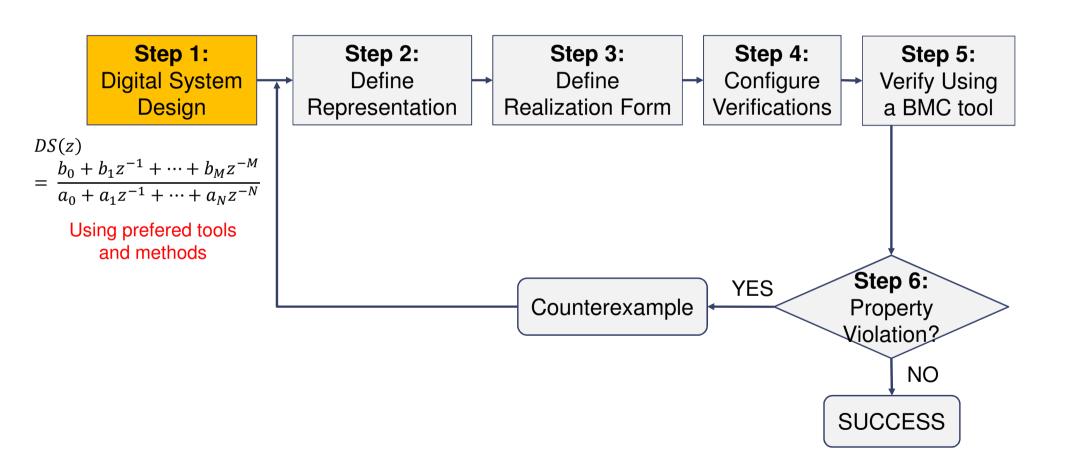

- Investigate FWL effects in fixed-point digital system (controllers and filters) implementations via BMC techniques

- Apply a design-aided verification methodology to digital systems, which is supported by the Digital-Systems Verifier (DSVerifier)

- Verify overflows, limit cycles, time constraints, stability, and mimimum phase in digital systems using standard benchmarks

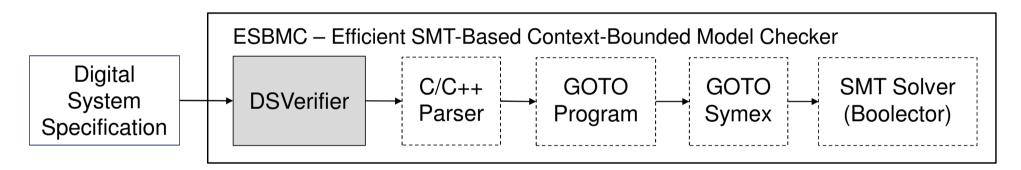

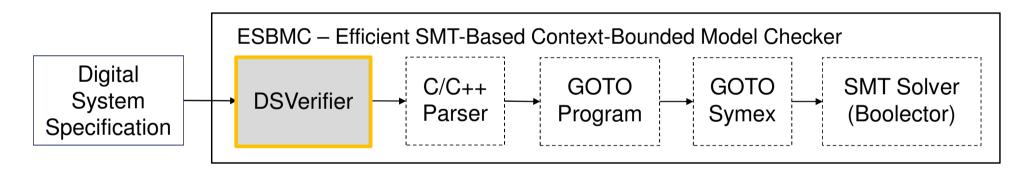

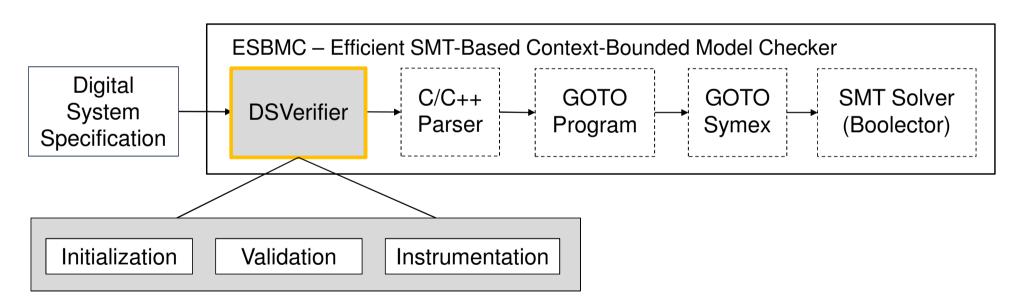

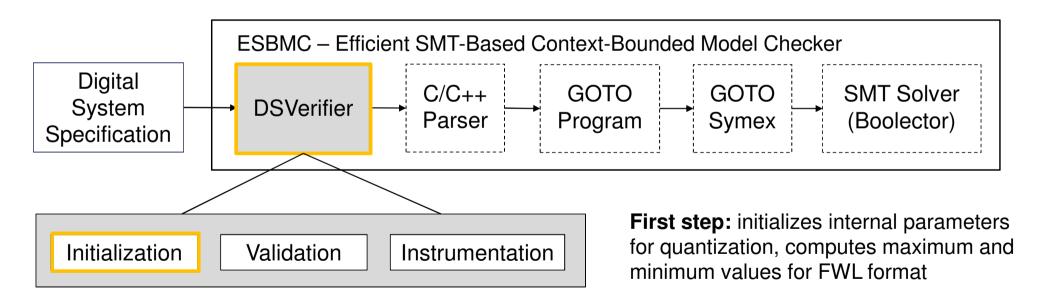

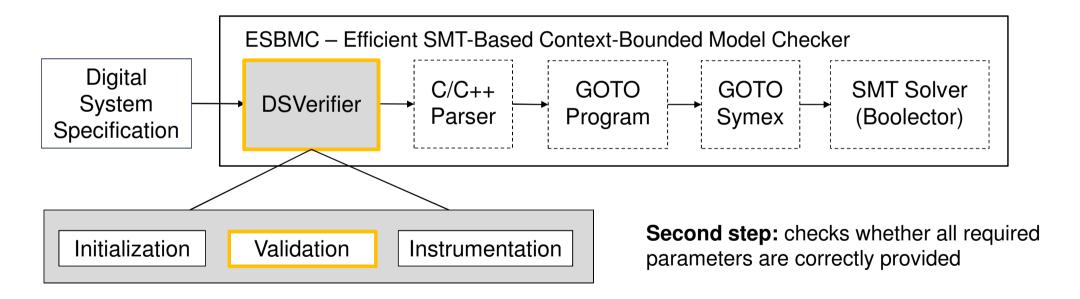

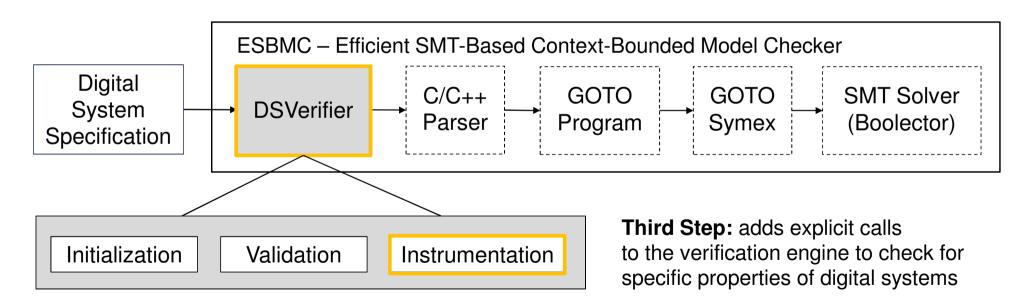

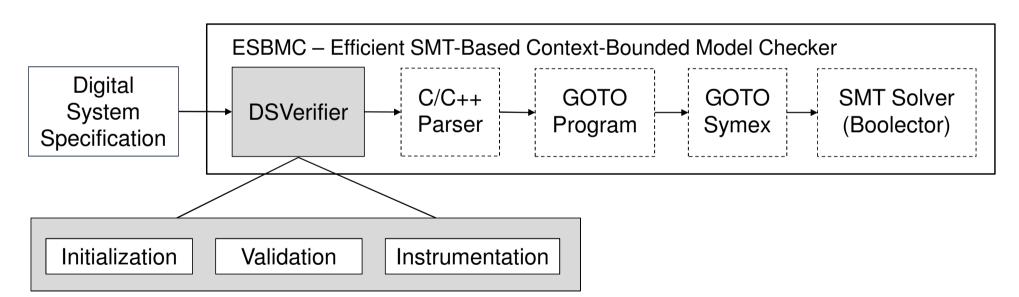

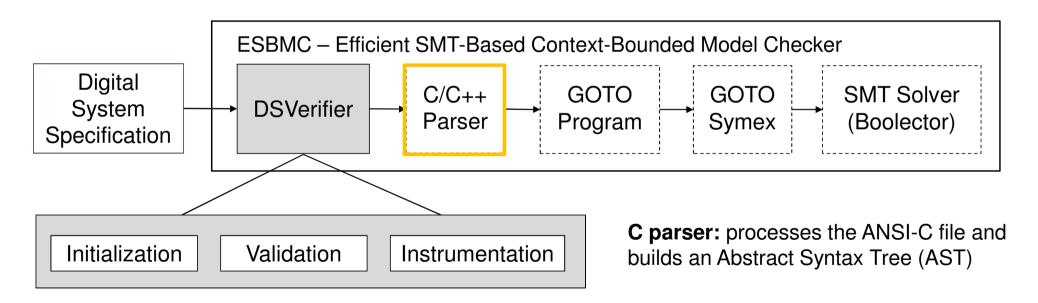

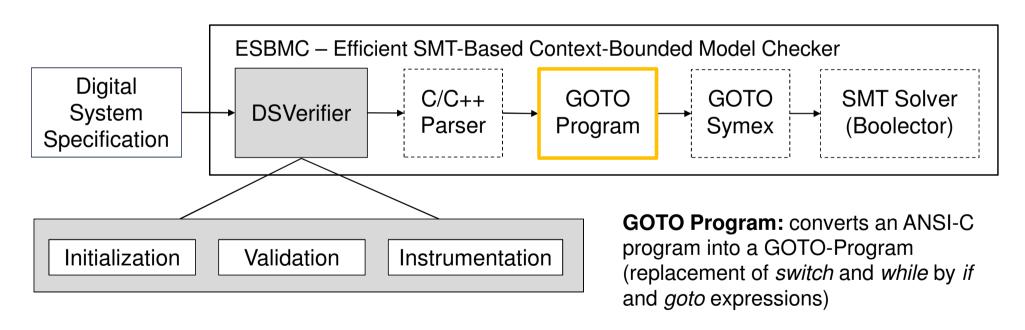

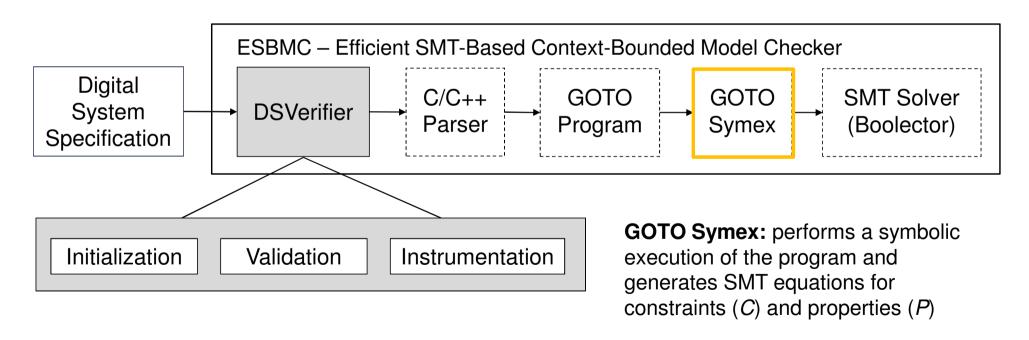

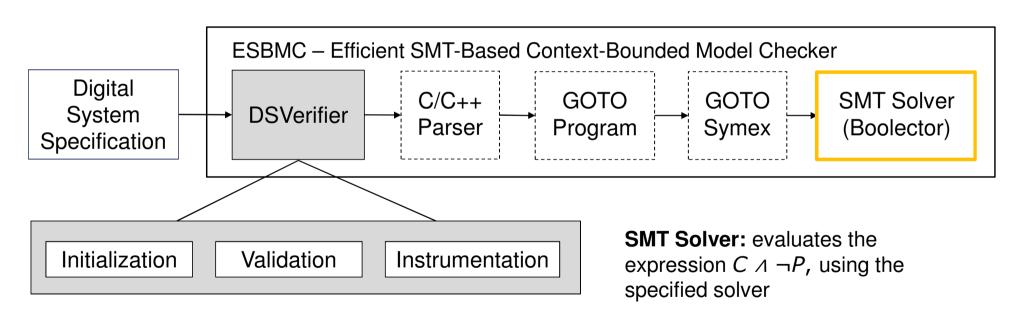

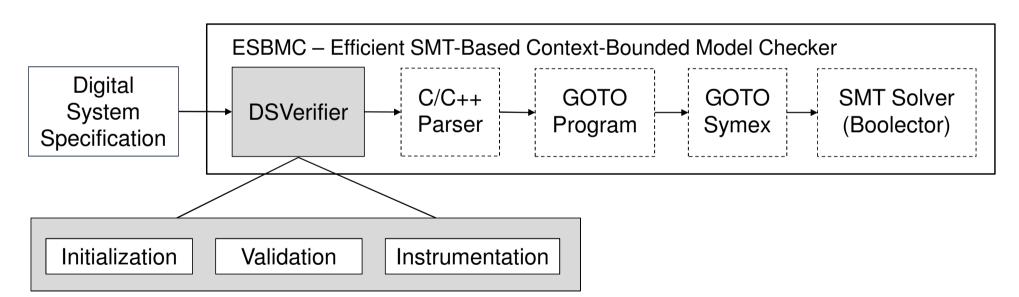

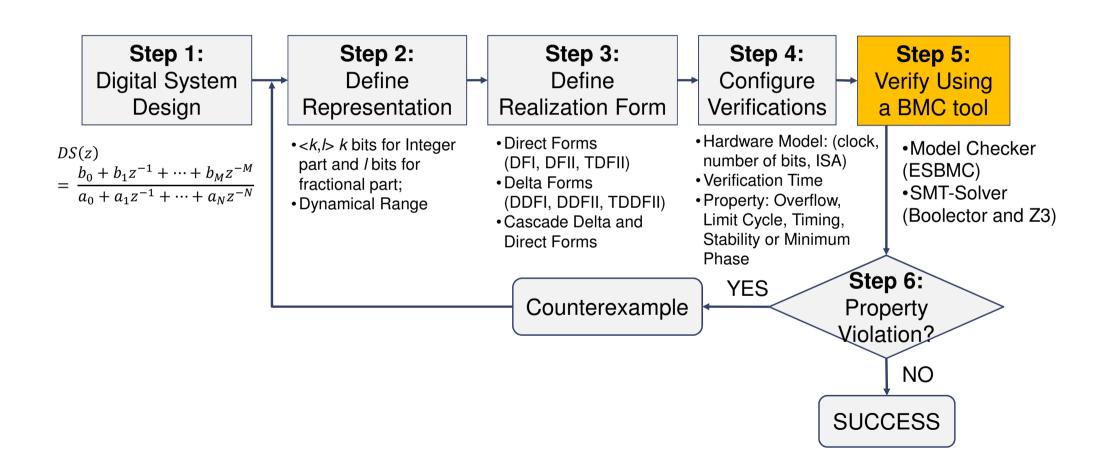

DSVerifier is an additional module for the Efficient SMT-based Context-Bounded Model Checker (ESBMC) to add support for digital systems verification

The complete tool includes four components from ESBMC

C Parser, GOTO Program, GOTO Symex, and SMT Solver

DSVerifier is an additional module for the Efficient SMT-based Context-Bounded Model Checker (ESBMC) to add support for digital systems verification

**DSVerifier module is included before the ANSI-C parser,** which provides functions related to quantization, digital-system realizations, and property verification

#### **DSVerifier Features**

- DSVerifier supports five verification properties, considering three directand delta-form implementations, in addition to the cascade form

- 1. Overflow: if a sum or product exceeds the number representation

- 2. Limit Cycle: checks for zero-input limit cycles, for any initial condition

- 3. Stability: considers FWL effects on pole locations

- 4. Minimum phase: considers FWL effects on zero locations

- Time constraints: checks whether a specific realization meets time constraints

Re-choose the numeric format and/or realization form

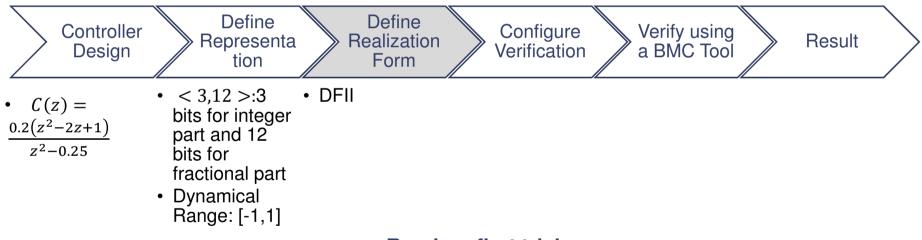

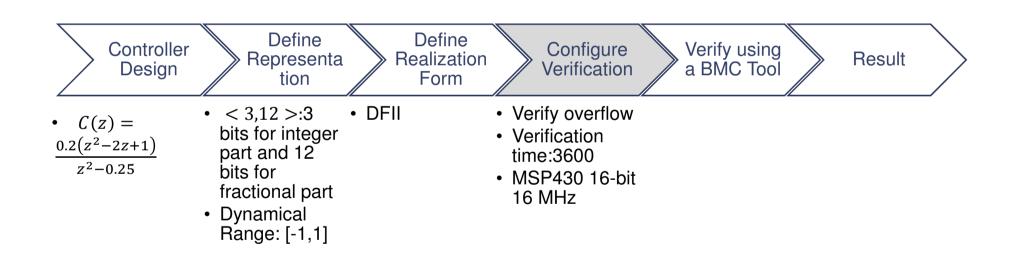

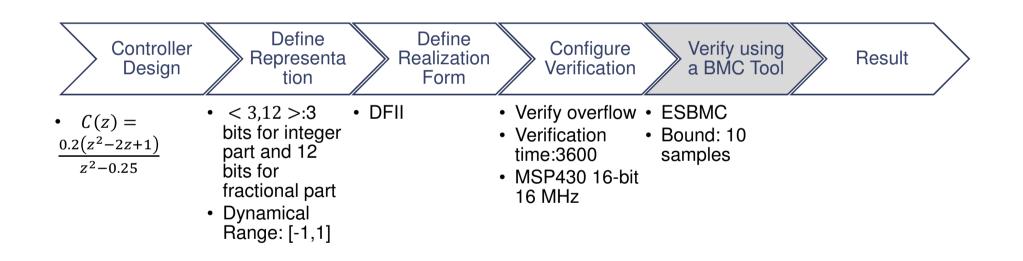

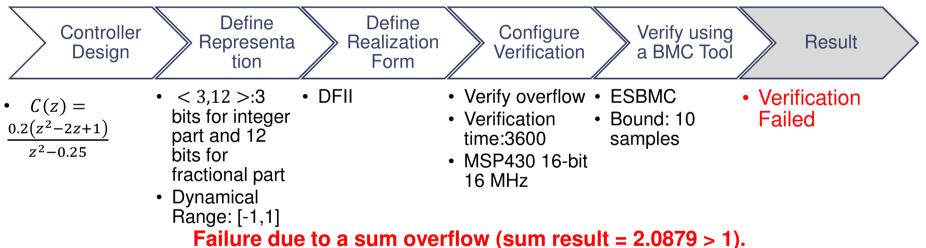

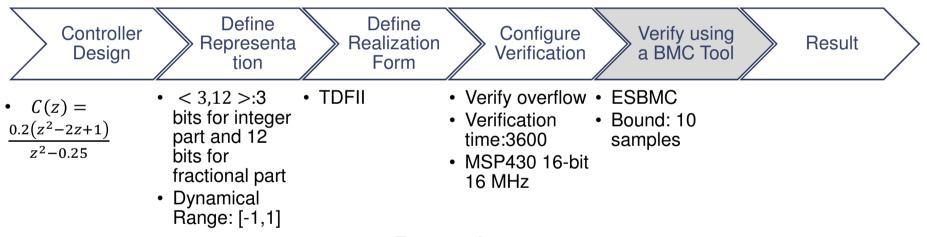

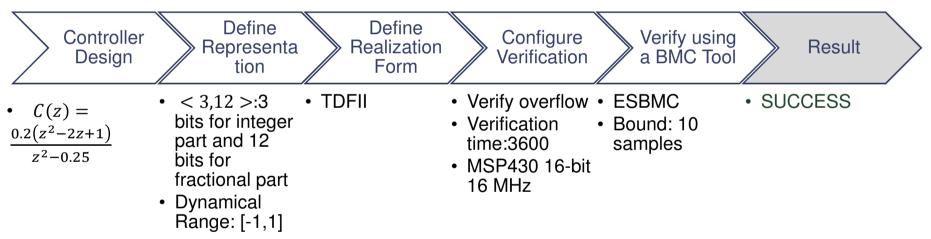

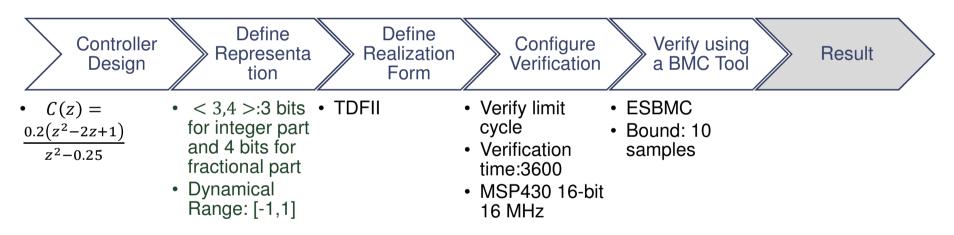

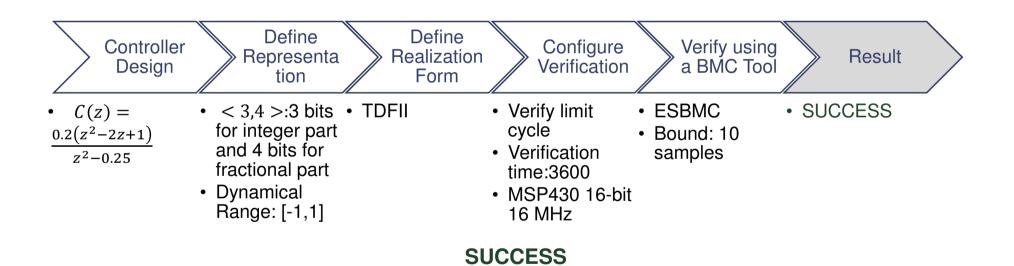

•  $C(z) = \frac{0.2(z^2 - 2z + 1)}{z^2 - 0.25}$

- $C(z) = \frac{0.2(z^2 2z + 1)}{z^2 0.25}$

- < 3,12 >:3

bits for integer part and 12

bits for fractional part

- Dynamical Range: [-1,1]

Numeric format choosen based on impulse response sum and hardware limitations

**Random first trial**

Input sequence: {0.9995, -0.9995, 0.9995, 1, 1, 1, 0.9995, 0.9995, 0.9995, 0.9995, 1}

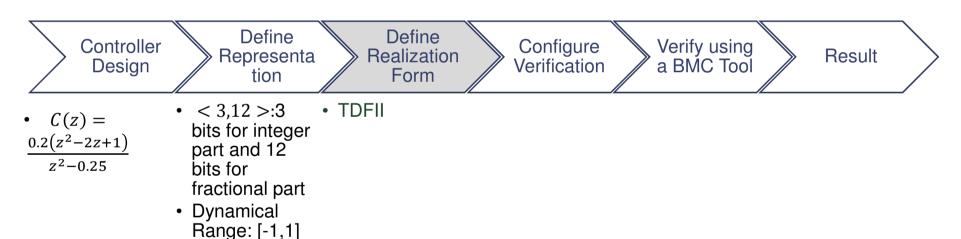

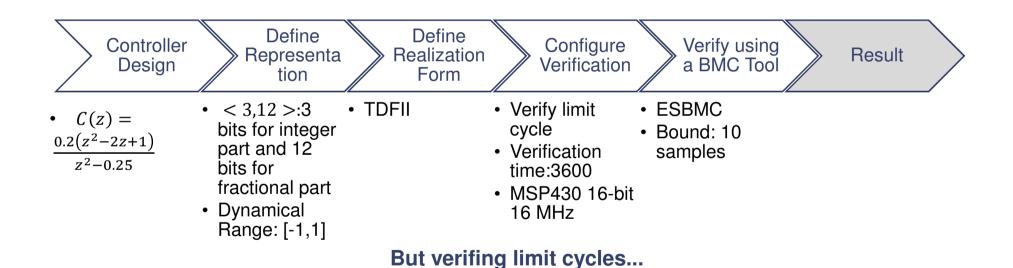

Redefine the implementation!

- $C(z) = \frac{0.2(z^2 2z + 1)}{z^2 0.25}$

- < 3,12 >:3

bits for integer

part and 12

bits for

fractional part

- Dynamical Range: [-1,1]

**Maintain the Representation**

**Change the Realization Form TDFII presents less sums and products**

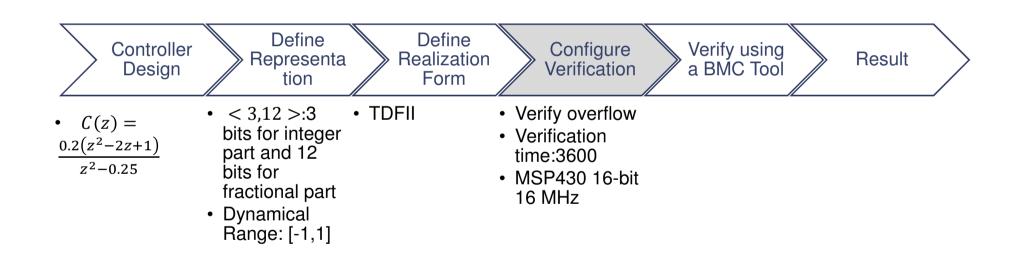

Repeat the test

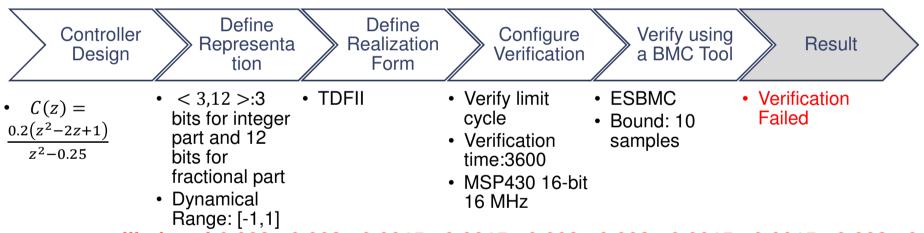

The problem was solved

Appears an oscillation: {-0.002, -0.002, -0.0015, -0.0015, -0.002, -0.002, -0.0015, -0.0015, -0.002}.

Zero input sequence

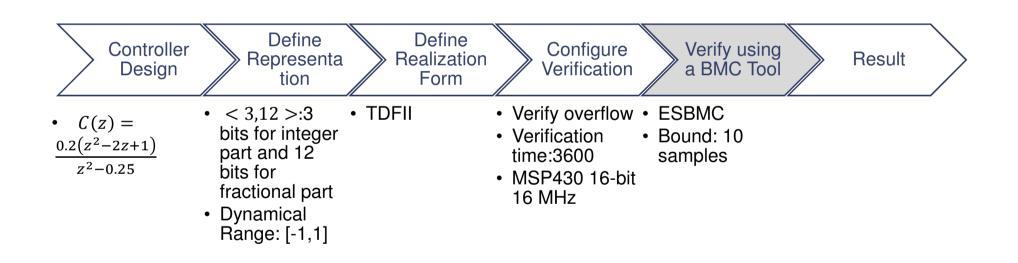

Redefine the implementation!

Verifying with a different representation...

There is a trade off: the oscillation is solved; however, there is an accurate loss

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

**Numerator Coefficients**

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

Number of Coefficients

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

$$H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}$$

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

```

**Denominator Coefficients**

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

implementation impl = {

.int_bits = 4,

.frac_bits = 10,

.min = -5,

.max = 5

};

```

Implementation aspects:

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

implementation impl = {

.int_bits = 4,

.frac_bits = 10,

.min = -5,

.max = 5

};

```

Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

implementation impl = {

.int_bits = 4,

.frac_bits = 10,

.min = -5,

.max = 5

};

```

Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

Dynamical Range: between -5.0 and 5.0

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

implementation impl = {

.int_bits = 4,

.frac_bits = 10,

.min = -5,

.max = 5

};

```

#### Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

Dynamical Range: between -5.0 and 5.0

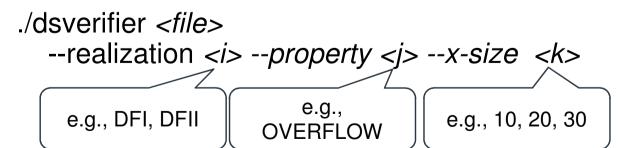

```

./dsverifier <file>

--realization <i>--property <j>--x-size <k>

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

# #include <dsverifier.h> digital\_system ds = { .b = {2.813, -0.0163, -1.872}, .b\_size = 3, .a = { 1.0, 1.068, 0.1239 }, .a\_size = 3 }; implementation impl = { .int\_bits = 4, .frac\_bits = 10, .min = -5, .max = 5 };

#### Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

Dynamical Range: between -5.0 and 5.0

```

./dsverifier <file>

--realization <i>--property <j>--x-size <k>

e.g., DFI, DFII

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

```

#include <dsverifier.h>

digital_system ds = {

.b = {2.813, -0.0163, -1.872},

.b_size = 3,

.a = { 1.0, 1.068, 0.1239 },

.a_size = 3

};

implementation impl = {

.int_bits = 4,

.frac_bits = 10,

.min = -5,

.max = 5

};

```

#### Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

Dynamical Range: between -5.0 and 5.0

```

./dsverifier <file>

--realization <i>--property <j>--x-size <k>

e.g., DFI, DFII

OVERFLOW

```

- The user provides the digital-system specification via an ANSI-C file

- Consider the following digital system:

```

H(z) = \frac{2.813z^2 - 0.0163z - 1.872}{z^2 + 1.068z + 0.1239}

```

# #include <dsverifier.h> digital\_system ds = { .b = {2.813, -0.0163, -1.872}, .b\_size = 3, .a = { 1.0, 1.068, 0.1239 }, .a\_size = 3 }; implementation impl = { .int\_bits = 4, .frac\_bits = 10, .min = -5, .max = 5

#### Implementation aspects:

14-bits architecture: 4 bits for integer and10 bits for precision parts

Dynamical Range: between -5.0 and 5.0

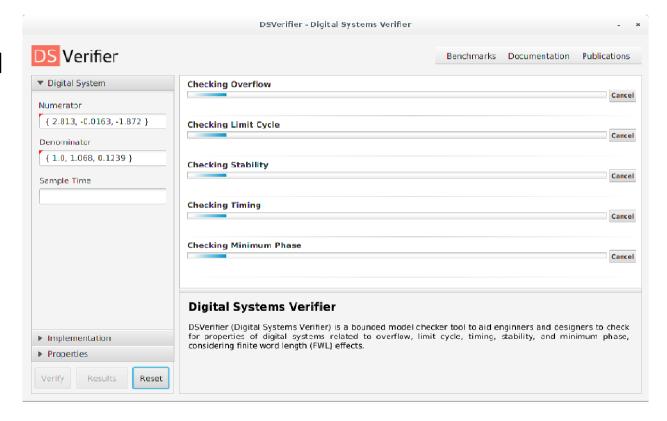

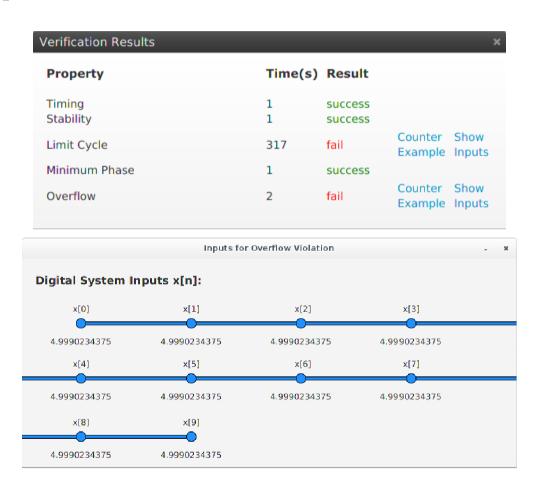

# DSVerifier Usage (Graphical User Interface)

- The graphical user interface (GUI) improves usability and attracts more digital-system enginners

- Allows users to provide all required parameters for the verification

- Parallel execution of verification tasks, which is guided by properties

# **DSVerifier Usage (Graphical User Interface)**

- Graphical verification results and counterexamples

- Access the documentation, benchmarks, and publications

- Developed using JavaFX

- Requires Java Runtime Environment Version 8.0 Update 40 (jre1.8.0 40)

#### **Conclusions**

- DSVerifier is able to verify digital systems and supports an extensive verification of different properties and realization forms

- DSVerifier can be regarded as an automated and reliable tool if compared to traditional simulation tools

- An enginner can verify during design phase, if the digital-system presents the expected behavior

#### **Future Work**

- Support for closed-loop system verification, more system-level properties, realizations, hardware platforms, and BMC tools

- Source code, benchmarks, experimental results, and publications are available at http://www.dsverifier.org

#### **Demonstration**